A Study on Neutral-Point Potential in Three-Level NPC Converters

Abstract

:1. Introduction

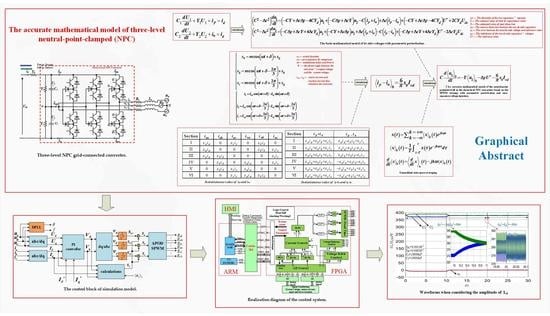

2. Operation and Principles

2.1. Main Circuit Topology

2.2. Modulation Strategy

2.3. AC-Side Current Control

3. Dynamic Model

3.1. Basic Mathematical Equations

- (1)

- The carrier frequency is much larger than that of the modulation signal.

- (2)

- There is no harmonic component in the reference output current.

3.2. Instantaneous Value of ip + in and ip − in

3.3. The Neutral-Point Potential Model

4. DC Voltage Control

4.1. Balancing Control

4.2. Calculating the Value of Ivd

5. Simulation and Experiment

5.1. Simulation Analysis

5.1.1. Accuracy of Equation (39)

5.1.2. DC Voltage Balancing Control

5.2. Experimental Verification

6. Conclusions

- (1)

- The basic reason for the neutral-point potential drift is the uneven shunt loss caused by parametric perturbation, and the capacitance error has no influence on it.

- (2)

- Zero-sequence voltage can be used to control the potential drift with the combination of the active current of the converter.

- (3)

- The total shunt loss, which is related to the output voltages and currents of the converter, is inversely proportional to the stable drift potential value.

- (4)

- The total DC capacitance has no influence on the stable drift potential value, but it affects the dynamic performance and amplitude of the third component.

Author Contributions

Funding

Conflicts of Interest

References

- Gui, S.; Lin, Z.; Huang, S. A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters. Energies 2015, 8, 2032–2047. [Google Scholar] [CrossRef] [Green Version]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors Voltage Switching Ripple in Three-Phase Three-Level Neutral Point Clamped Inverters with Self-Balancing Carrier-Based Modulation. Energies 2018, 11, 3244. [Google Scholar] [CrossRef]

- Wu, M.; Song, Z.; Lv, Z.; Zhou, K.; Cui, Q. A Method for the Simultaneous Suppression of DC Capacitor Fluctuations and Common-Mode Voltage in a Five-Level NPC/H Bridge Inverter. Energies 2019, 12, 779. [Google Scholar] [CrossRef]

- Son, Y.; Kim, J. A Novel Phase Current Reconstruction Method for a Three-Level Neutral Point Clamped Inverter (NPCI) with a Neutral Shunt Resistor. Energies 2018, 11, 2616. [Google Scholar] [CrossRef]

- Kang, K.P.; Cho, Y.; Ryu, M.H.; Baek, J.W. A Harmonic Voltage Injection Based DC-Link Imbalance Compensation Technique for Single-Phase Three-Level Neutral-Point-Clamped (NPC) Inverters. Energies 2018, 11, 1886. [Google Scholar] [CrossRef]

- In, H.C.; Kim, S.M.; Lee, K.B. Design and Control of Small DC-Link Capacitor-Based Three-Level Inverter with Neutral-Point Voltage Balancing. Energies 2018, 11, 1435. [Google Scholar] [CrossRef]

- Celanovic, N.; Boroyevich, D. A comprehensive study of neutralpoint voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters. IEEE Trans. Power Electron. 2000, 15, 242–249. [Google Scholar] [CrossRef]

- Pou, J.; Pindado, R.; Boroyevich, D.; Rodríguez, P. Evaluation of the low-frequency neutral-point voltage oscillations in the three-level inverter. IEEE Trans. Ind. Electron. 2005, 56, 1582–1588. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Shen, J.; Schroder, S.; Rosner, R.; El-Barbari, S. A comprehensive study of neutral-point self-balancing effect in neutral-point-clamped three-level inverters. IEEE Trans. Power Electron. 2011, 26, 3084–3095. [Google Scholar] [CrossRef]

- Hu, C.G.; Holmes, G.; Shen, W.X.; Yu, X.B.; Wang, Q.J.; Luo, F.L. Neutral-point potential balancing control strategy of three-level active NPC inverter based on SHEPWM. IET Power Electron. 2017, 10, 1755–4535. [Google Scholar] [CrossRef]

- Stala, R. Application of balancing circuit for DC-link voltages balance in a single-phase diode-clamped inverter with two three-level legs. IEEE Trans. Ind. Electron. 2011, 58, 4185–4195. [Google Scholar] [CrossRef]

- Du Toit Mouton, H. Natural balancing of three-level neutral-point clamped PWM inverters. IEEE Trans. Ind. Electron. 2002, 49, 1017–1025. [Google Scholar] [CrossRef]

- Von Jouanne, A.; Dai, S.; Zhang, H. A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and common mode voltage elimination. IEEE Trans. Ind. Electron. 2002, 49, 739–745. [Google Scholar] [CrossRef]

- Pou, J.; Pindado, R.; Boroyevich, D.; Rodriguez, P. Limits of the neutral-point balance in back-to-back-connected three-level converters. IEEE Trans. Power Electron. 2004, 19, 722–731. [Google Scholar] [CrossRef]

- Kanchan, R.S.; Tekwani, P.N.; Gopakumar, K. Three-level inverter scheme with common mode voltage elimination and DC link capacitor voltage balancing for an open-end winding induction motor drive. IEEE Trans. Power Electron. 2006, 21, 1676–1683. [Google Scholar] [CrossRef]

- Wu, D.; Wu, X.; Su, L.; Yuan, X.; Xu, J. A dual three-level inverter-based open-end winding induction motor drive with averaged zero-sequence voltage elimination and neutral-point voltage balance. IEEE Trans. Ind. Electron. 2016, 63, 4783–4795. [Google Scholar] [CrossRef]

- Liu, G.; Wang, D.F.; Wang, M.R.; Zhu, C.; Wang, M.Y. Neutral-Point Voltage Balancing in Three-Level Inverters Using an Optimized Virtual Space Vector PWM With Reduced Commutations. IEEE Trans. Ind. Electron. 2018, 65, 6959–6969. [Google Scholar] [CrossRef]

- Jiang, W.D.; Wang, L.; Wang, J.P.; Zhang, X.W.; Wang, P.X. A Carrier-Based Virtual Space Vector Modulation with Active Neutral-Point Voltage Control for a Neutral-Point-Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2018, 65, 8687–8696. [Google Scholar]

- Jiao, Y.; Lee, F.C.; Lu, S. Space vector modulation for three-level NPC converter with neutral point voltage balance and switching loss reduction. IEEE Trans. Power Electron. 2014, 29, 5579–5591. [Google Scholar] [CrossRef]

- Bhat, A.H.; Langer, N. Capacitor voltage balancing of three-phase neutral-point-clamped rectifier using modified reference vector. IEEE Trans. Power Electron. 2014, 29, 561–568. [Google Scholar] [CrossRef]

- Choi, U.M.; Lee, K.B. Space vector modulation strategy for neutral-point voltage balancing in three-level inverter systems. IET Power Electron. 2013, 6, 1390–1398. [Google Scholar] [CrossRef]

- Lyu, J.; Hu, W.; Wu, F.; Yao, K.; Wu, J. Variable modulation offset SPWM control to balance the neutral-point voltage for three-level inverters. IEEE Trans. Power Electron. 2015, 30, 7181–7192. [Google Scholar] [CrossRef]

- Li, J.; Liu, J.; Boroyevich, D.; Mattavelli, P.; Xue, Y. Three-level active neutral-point-clamped zero-current-transition converter for sustainable energy systems. IEEE Trans. Power Electron. 2011, 26, 3680–3693. [Google Scholar] [CrossRef]

- Wu, Y.; Shafi, M.; Knight, A.; McMahon, R. Comparison of the effects of continuous and discontinuous PWM schemes on power losses of voltage-sourced inverters for induction motor drives. IEEE Trans. Power Electron. 2011, 26, 182–191. [Google Scholar] [CrossRef]

- Zhang, D.; Wang, F.; Burgos, R.; Boroyevich, D. Common mode circulating current control of paralleled interleaved three-phase two-level voltage-source converters with discontinuous space-vector modulation. IEEE Trans. Power Electron. 2011, 26, 3925–3935. [Google Scholar] [CrossRef]

- Hou, C.C.; Shih, C.C.; Cheng, P.T.; Hava, A.M. Common-mode voltage reduction pulse width modulation techniques for three-phase grid connected converters. IEEE Trans. Power Electron. 2013, 28, 1971–1979. [Google Scholar] [CrossRef]

- Zhang, M.; Chi, B.; Wang, X.; Wang, Q.; Li, G. Study on neutral-point potential control for the NPC three-level converter. In Proceedings of the 2016 IEEE 11th Conference on Industrial Electronics and Applications (ICIEA), Hefei, China, 5–7 June 2016. [Google Scholar]

- Schauder, C.; Mehta, H. Vector analysis and control of advanced static Var compensators. IEE Proc. C-Gener. Transm. Distrib. 1993, 140, 299–306. [Google Scholar] [CrossRef]

- Zhang, M.; Wang, T.; Wang, X.; Wang, Q.; Li, G. Study on Neutral-point Potential Control for the APF Based on NPC Three-level Inverter. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018. [Google Scholar]

- Yazdani, A.; Iravani, R. A generalized state-space averaged model of the three-level NPC converter for systematic DC-voltage-balancer and current-controller design. IEEE Trans. Power Deliv. 2005, 20, 1105–1114. [Google Scholar] [CrossRef]

| Section | ipa | ipb | ipc | ina | inb | inc |

|---|---|---|---|---|---|---|

| 1 | saia | 0 | scic | 0 | sbib | 0 |

| 2 | saia | 0 | 0 | 0 | sbib | scic |

| 3 | saia | sbib | 0 | 0 | 0 | scic |

| 4 | 0 | sbib | 0 | saia | 0 | scic |

| 5 | 0 | sbib | scic | saia | 0 | 0 |

| 6 | 0 | 0 | scic | saia | sbib | 0 |

| Section | ip + in | ip − in |

|---|---|---|

| 1 | saia + sbib + scic | saia − sbib + scic |

| 2 | saia + sbib + scic | saia − sbib − scic |

| 3 | saia + sbib + scic | saia + sbib − scic |

| 4 | saia + sbib + scic | −saia + sbib − scic |

| 5 | saia + sbib + scic | −saia + sbib + scic |

| 6 | saia + sbib + scic | −saia − sbib + scic |

| Parameters | Value | Parameters | Value |

|---|---|---|---|

| Line voltage (rms) | 380 V | Line frequency | 50 Hz |

| Short-circuit capacity | 50 MVA | X/R Ratio | 7 |

| Carrier frequency | 9.6 kHz | U* | 380 V |

| Ls | 0.3 mH | Rs | 0.01 Ω−1 |

| Udc | 760 V | Rd | 0.002 Ω−1 |

| Figure 6 | Δy/Ω−1 | Δc/uF | Y/Ω−1 | C/uF | 〈u2〉0/V (Simulation) | 〈u2〉0/V (Calculated) |

|---|---|---|---|---|---|---|

| (a) | 0 | 0 | 2YP + 0.002 | 20,000 | 0 | 0 |

| (b) | 0 | 5000 | 2YP + 0.002 | 20,000 | 0 | 0 |

| (c) | 0.001 | 0 | 2YP + 0.002 | 20,000 | −34.5 | |

| (d) | −0.001 | 0 | 2YP + 0.002 | 20,000 | 34.5 | 34.5 |

| (e) | 0.0005 | 0 | 2YP + 0.002 | 20,000 | −18.5 | −17.3 |

| (f) | 0.0015 | 0 | 2YP + 0.002 | 20,000 | −49.6 | −51.7 |

| (g) | 0.001 | 0 | 2YP + 0.004 | 20,000 | −29.5 | −29.2 |

| (h) | 0.001 | 0 | 2YP + 0.002 | 10,000 | −35.0 | −34.5 |

| Figure 8 | s0 | Ivd/A | Ivq/A | Δy/Ω−1 | 〈u2〉0/V (Simulation) | Yp/Ω−1 (Estimated) | 〈u2〉0/V (Calculated) |

|---|---|---|---|---|---|---|---|

| (a) | 0.002 | 40.8 | 0 | 0 | −12.6 | 0.0052 | |

| (b) | −0.002 | 40.8 | 0 | 0 | 12.6 | 12.6 | |

| (c) | 0.001 | 40.8 | 0 | 0 | −6.5 | −6.3 | |

| (d) | 0.004 | 40.8 | 0 | 0 | −25.0 | −25.2 | |

| (e) | 0.004 | −40.8 | 0 | 0 | 6.2 | 0.0241 | |

| (f) | 0.004 | −40.8 | 0 | 0.00082 | −0.3 | 0 | |

| (g) | 0.01 | 0 | 40.8 | 0 | 0.3 | ||

| (h) | 0.02 | 0 | 40.8 | 0 | 0.6 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Cui, Y.; Wang, Q.; Tao, J.; Wang, X.; Zhao, H.; Li, G. A Study on Neutral-Point Potential in Three-Level NPC Converters. Energies 2019, 12, 3367. https://doi.org/10.3390/en12173367

Zhang M, Cui Y, Wang Q, Tao J, Wang X, Zhao H, Li G. A Study on Neutral-Point Potential in Three-Level NPC Converters. Energies. 2019; 12(17):3367. https://doi.org/10.3390/en12173367

Chicago/Turabian StyleZhang, Maosong, Ying Cui, Qunjing Wang, Jun Tao, Xiuqin Wang, Hongsheng Zhao, and Guoli Li. 2019. "A Study on Neutral-Point Potential in Three-Level NPC Converters" Energies 12, no. 17: 3367. https://doi.org/10.3390/en12173367